# THESIS / THÈSE

#### **MASTER IN COMPUTER SCIENCE**

Automata oriented program verification

Grégoire, Bertrand

Award date: 2002

Link to publication

**General rights**Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 10. May. 2024

FUNDP Institut d'Informatique

Rue Grandgagnage, 21 B - 5000 NAMUR (Belgique)

### Automata Oriented Program Verification

Bertrand Grégoire

Under the advisory of Prof. Pierre-Yves Schobbens

Institut d'Informatique Facultés Universitaires Notre-Dame de la Paix Namur

Septembre 2002

#### Abstract

The formal verification process of a design with respect to temporal specifications is essential while designing (reactive) systems.

The process we present here relies on timed Live Sequence Charts (LSCs) to describe properties of the system under development. The LSCs are unwound into timed automata and automatically verified with a fair CTL model checker. We describe all the transitions that take part in this completely automatic process.

To obtain a more efficient verification we introduce a new class of automata, which is proven to be an interesting subset of the timed Büchi automata, and show, theoretically and algorithmically, how the efficient verification of these properties can be conducted using the VIS model checker.

**Keywords** formal verification, model checking, reactive system, temporal requirement, VIS, invariant check, timed automaton, non-failure acceptance.

#### Abstract

Il est essentiel, lors de la mise en place de systèmes réactifs, de pouvoir vérifier des propriétés temporelles dès les premières phases du développement.

Le processus de vérification automatisé que nous décrivons ici se base sur des Live Sequence Charts (LSCs) pour décrire les propriétes attendues. Ces LSCs sont applatis en automates temporisés, et la propriéte est vérifiée automatiquement par un vérificateur de modèles CTL équitable. Nous décrivons les traductions intermédiaires qui permettent cette vérification automatique.

Pour obtenir un processus plus efficace nous présentons une nouvelle classe d'automates, définie comme un sous-ensemble intéressant des automates temporisés de Büchi. Nous montrons comment une vérification efficace peut être conduite sur ces propriétés, en théorie et par une procédure concrète.

Mots-clés vérification formelle, vérification de modèles, système reactif, comportement temporel, VIS, vérification d'invariant, automate temporisé, acceptation sans-échec.

### Acknowledgements

I would like to thank Prof. Pierre-Yves Schobbens, Mr. Patrick Heymans and Mr. Yves Bontemps for giving me the opportunity to discover the world of research, guided with their great insight. They were available to answer my questions and their (many) remarks greatly helped me in my work.

Prof. Bernhard Josko welcomed me in his Embedded Systems departement, at Oldenburg. There, I collaborated with Hartmut Wittke, Jocken Klose and Tom Bienmüller on the subject presented here. I would like to especially thank them all for their help, in Oldenburg or during the writing of this thesis. They found place for me in their overfull agendas, and made a place for me at their table. Thanks to Ingo, Alexander, Thomas and Ulf for having made my stay and work easier.

My friends have made my time in Oldenburg fun, thanks Christian, Céline, Nadine, Mad, Victor, Marina, Tomas, Karer, Celia, Rebecca, Shantala, Udo, Ditza, Frank, Fathi and the many others. Annika gave me her Germany, Louis his energy and Imke her thousands different smiles.

I owe much of who I am to my parents. They have started me on this path, and have always been with me along the way. For all the support they gave me, I would like to thank wy whole family: Valérie, Alex, maman and papa. Thanks also to Opa for the funny time we spent together in Germany, and to nonkel Luc, for his valuable pieces of advice about my bad english.

Finally, I would like to thank my girlfriend, Barbara. She forgave me the time we couldn't spend together and encouraged me every time I needed it, even without saying a word.

# Contents

| 1 | Spe |        | on basics 7                                                            |

|---|-----|--------|------------------------------------------------------------------------|

|   | 1.1 | Introd | ${f uction\ to\ specification\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .}$ |

|   | 1.2 | Live S | equence Charts (LSCs)                                                  |

|   |     | 1.2.1  | The birth of LSCs                                                      |

|   |     | 1.2.2  | Formalism description                                                  |

|   |     | 1.2.3  | Constructs of the language                                             |

|   |     | 1.2.4  | LSC interpretation                                                     |

|   | 1.3 | Auton  | nata theory on infinite words                                          |

|   |     | 1.3.1  | Finite automata on infinite words                                      |

|   |     | 1.3.2  | Timed finite automata on infinite words 16                             |

|   |     | 1.3.3  | Timed Büchi automaton                                                  |

|   | 1.4 | Unwin  | ding LSCs into TBAs                                                    |

|   |     | 1.4.1  | Intuitive procedure                                                    |

|   |     | 1.4.2  | Pitfalls to the intuition                                              |

|   | 1.5 | Activa | tion modes                                                             |

|   |     | 1.5.1  | Initial mode                                                           |

|   |     | 1.5.2  | Invariant mode                                                         |

|   |     | 1.5.3  | Iterative mode                                                         |

|   | 1.6 | Partic | ular TBAs                                                              |

|   |     | 1.6.1  | Activation mode                                                        |

|   |     | 1.6.2  | Acyclic Automata                                                       |

|   |     | 1.6.3  | Remark on clocks                                                       |

|   | 1.7 | To con | nclude                                                                 |

| 2 | Mod | del Ch | ecking 31                                                              |

|   | 2.1 |        | uction to formal verification                                          |

|   |     | 2.1.1  | Like a candle in the dark                                              |

|   |     | 2.1.2  | The candle becomes lighthouse                                          |

|   |     | 2.1.3  | Automatic formal verification                                          |

|   | 2.2 | Tempo  | oral logics                                                            |

|   |     | 2.2.1  | Linear Temporal Logic (LTL)                                            |

|   |     | 2.2.2  | Computation Tree Logic (CTL)                                           |

|   |     | 2.2.3  | FairCTL                                                                |

|   | 2.3 |        | checking of temporal logic formulas                                    |

|   | -   | 2.3.1  | The choice between linear or branching paradigm 37                     |

|   |     | 2.3.2  | LTL model checking                                                     |

|   |     | 2.3.3  | CTL model checking                                                     |

|   |     | 2.3.4  | Language containment                                                   |

|   |     |        |                                                                        |

|   | 2.4  | Maturation of model checking                |          |

|---|------|---------------------------------------------|----------|

|   |      | 2.4.1 Composition                           |          |

|   |      | 2.4.2 Abstraction                           |          |

|   |      | 2.4.3 Symbolic model checking 4             |          |

|   |      | 2.4.4 Efficient LTL model checking 4        |          |

|   | 2.5  | Safety properties and invariance checking 4 |          |

|   |      | 2.5.1 Underlying intuition                  |          |

|   |      | 2.5.2 Checking invariants                   | 6        |

| 3 | Pra  | ctical model checking 4                     | -        |

|   | 3.1  | Model checking tools survey 4               | •        |

|   | 3.2  |                                             | 8        |

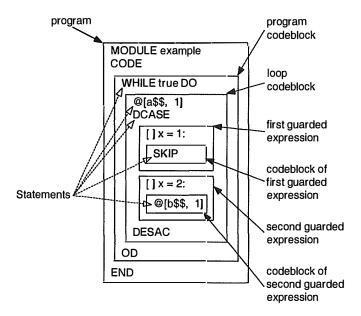

|   |      |                                             | 9        |

|   |      | 0 1                                         | 9        |

|   |      |                                             | 2        |

|   |      | 0 0 1                                       | 3        |

|   |      | · · · · · · · · · · · · · · · · · · ·       | 4        |

|   | 3.3  | The Statemate environment                   | 4        |

|   |      | · · · · · · · · · · · · · · · · · · ·       | 4        |

|   |      | 3.3.2 Semantics remarks                     | 6        |

|   | 3.4  | Approximations                              | 7        |

|   |      | 3.4.1 Specification restrictions 5          | 7        |

|   |      | 3.4.2 Environment approximations 5          | 8        |

| 4 | Fini | te acceptance on infinite words 6           | 1        |

|   | 4.1  | <del>-</del>                                | 1        |

|   |      | =                                           | 1        |

|   |      |                                             | 2        |

|   |      | <del>-</del>                                | 4        |

|   | 4.2  | Expressiveness theorem                      | 5        |

|   |      |                                             | 5        |

|   |      | 4.2.2 Clock algorithm                       | 7        |

|   |      |                                             | 0        |

|   |      |                                             | 1        |

|   | 4.3  |                                             | 1        |

|   |      |                                             | ·1       |

|   |      |                                             | -<br>1   |

|   |      |                                             | '3       |

|   | 4.4  |                                             | 4        |

| 5 | Rea  | l usage 7                                   | 5        |

| • | 5.1  |                                             | '5       |

|   | 5.2  |                                             | 6'       |

|   | 0.2  | 1                                           | 0<br>6'  |

|   |      | ,                                           | 0<br>7'  |

|   |      | •                                           | ،<br>7'  |

|   |      |                                             |          |

|   | ב ח  |                                             | '8<br>'0 |

|   | 5.3  |                                             | '8<br>'0 |

|   | 5.4  |                                             | '9<br>'0 |

|                  | 5.4.2 Semantics                            | 80 |

|------------------|--------------------------------------------|----|

|                  | 5.4.3 Propositional architecture           | 81 |

|                  | 5.4.4 Available optimizations              | 81 |

|                  | 5.5 Translation of TBAs into SMI           | 82 |

|                  | 5.5.1 Core automaton                       | 82 |

|                  | 5.5.2 Activation part                      |    |

|                  | 5.5.3 Correctness                          |    |

|                  | 5.6 Final steps before model checking      |    |

|                  | 5.7 Conclusion                             | 90 |

| 6                | Results                                    | 91 |

|                  | 6.1 Specification support                  | 91 |

|                  | 6.1.1 LSC                                  |    |

|                  | 6.1.2 LTL                                  |    |

|                  | 6.2 More efficient verification            |    |

|                  | 6.3 Iterative activation mode              |    |

|                  | 6.4 Witness verification                   | 92 |

| 7                | Conclusion                                 | 93 |

| $\mathbf{A}_{1}$ | ppendices                                  | a  |

| A                | LSC unwinding                              | a  |

| В                | Statemate model certifier patterns library | g  |

|                  | -                                          | •  |

# List of Figures

| 1                                                                   | Transformational and reactive systems     |

|---------------------------------------------------------------------|-------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.10 | LSC example                               |

| 2.1<br>2.2                                                          | A binary decision tree                    |

| 3.1<br>3.2<br>3.3<br>3.4                                            | VIS overview                              |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                                     | A constrained automaton                   |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                | Verification environment at CvOU          |

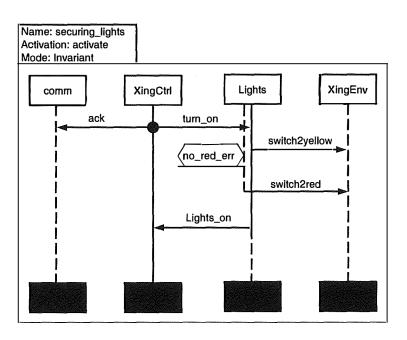

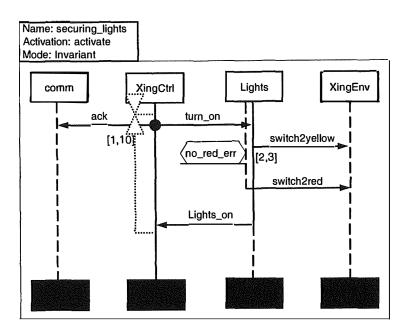

| A.1<br>A.2                                                          | A LSC property of the crossing controller |

| A.3 | The unwound TBA                      | d |

|-----|--------------------------------------|---|

| A.4 | SMI property translation(1)          | e |

| A.5 | SMI property translation(2)          | f |

| B.1 | The Statemate activation modes       | h |

|     | The automaton of a STATEMATE pattern |   |

The news group comp.risk is full of funny stories, such as the one reported in [Mur90], a British news paper. A runaway train went down the London's Tube track, leaving its driver standing behind, on the platform. The man actually left the cab of his fully-automated train to check a door which had failed to close properly. When the door did shut an electrical circuit was completed and the train, with 20 passengers on board, moved off before the driver had time to rush back to the controls. None where killed nor injured, but the driver has been sacked.

According to a U.S. Army report, a software problem contributed to digging holes at Fort Drum, in June 2002. Two soldiers were firing artillery shells, relying on the output of the Advanced Field Artillery Tactical Data System. But if one forget to enter the target's altitude, the system assumes a default of 0, when (part of) Fort Drum is at 679 feet above sea level. The report goes on to warn that soldiers should not depend exclusively on this one system, and should use other computers or manual calculations.

Software failures, and so are these unexpected behaviors, are a nightmare of many major firms. Let us just remember the paranoia we faced with the so called "Year 2000-Related" computer failures.

Unfortunately many human lives rely on software or hardware systems, which control airplanes, automobiles, nuclear power plants and medical laboratories, among others. These systems are called *safety-critical systems*. This designation regroups computer, electronic or electromechanical systems whose failure may cause injury or death to human beings.

### Transformational and reactive systems

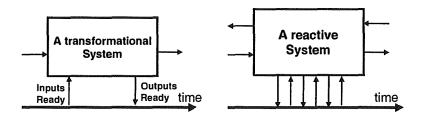

Most safety-critical systems are highly *reactive*, meaning they interact with their environment. The systems which are not reactive are transformational, we illustrate both systems behaviors in figure 1.

Transformational systems are those which have all inputs ready when invoked and the outputs are produced after a certain computation period. Most industrial processes are transformational systems, but a simple procedure that computes the square root of a number is a transformational process as well.

The reason a *reactive* system exists is typically to collaborate or interact with some entities in its environment. Sending, receiving, recognizing and subjecting sequences of symbols are parts of a reactive behavior. A well understood

reactive system is a traffic-light controller. It is virtually impossible to write a transformational program that implements such a controller, since the inputs occur when the system is already running. In fact, most controllers are by definition reactive, with application domains ranging from process control, military, aerospace, and automotive applications to medical electronics, and similar embedded systems.

Amir Pnueli [Pnu77] calls "reactive systems" any nonterminating or continuously operating concurrent programs, such as operating systems or network protocols. The use of such systems is growing year after year. Graphical user interface based software (GUI) and embedded systems are typically reactive. The latter is often implemented as hardware.

Figure 1: Transformational and reactive systems

#### Formal methods

The design error problem of life-critical (reactive) systems is a great threat to the human being. There are 3 basic strategies [Hol97] for dealing with design errors:

#### 1. Testing (lots of!).

The problem with life testing is that in order to measure ultra-reliability one must test for exorbitant amounts of time.

#### 2. Design diversity (fault-tolerant software).

The basic idea is to use separate design/implementation teams to produce multiple versions from the same specification. Then, non-exact threshold voters are used to mask the effect of a design error in one of the versions. The underlying hope is that the design flaws will manifest errors independently, or nearly so. In fact, design diversity can create an "illusion" of ultra-reliability, without actually providing it.

3. Fault avoidance (formal specification and verification, reusable modules)

Formal methods may be used to specify and model the behavior of a system and to mathematically verify that the system design and implementation satisfy system functional and safety properties.

The often targeted  $1-10^{-9}$  reliability is beyond the range of quantification (for both testing and design diversity) as stated in [Hol97]. We have hence no other choice than to develop safety-critical systems in the most rigorous manner available to us, which is the use of formal methods. We use the term *formal methods* to refer to the variety of mathematical modeling techniques that are applicable to computer system (software and hardware) design.

### The formal specification challenge

Designers of today's reactive systems face design challenges of enormous complexity due to the increase of design content, explosion of features, ambiguous design parameters and evolving customer requirements.

A high-level (formal) specification written in a language that has a well defined semantics is mandatory for such designs. Nevertheless many companies still use hand-written (informal) specifications. Benefits of a formal specification compared with an informal one are very similar to the benefits of a true, working, program compared with a document describing what the program should do. The first is a usable object, while the later is nothing but a nice piece of paper that needs to be used by a human. Non formal methods of communication often leads to costly design and debug iterations [BF93]. Numerous studies have shown that correcting an error during integration costs over 10 to 1000 times more than correcting it at specification time.

The challenge of generating complete and unambiguous specifications is, of course, only half the battle. The other big unknown is whether the specifications accurately reflect user requirements [Gil97].

The formulation of requirements into a formal specification is called *synthesis*. Traditionally, methodologies were used to produce the model, based on experience in industry [BP94]. More recently, development environments provide automatic specifications synthesis, based on scenarios [I-L00b].

### The formal verification challenge

Once we have got a formal representation of both the design under development and the requirements (specifications) we are excepting from it, it is time to check whether the first fulfills the later. This problem is called the *verification*, or *validation* process.

Many techniques have been studied for the past twenty years, developing a wide range of approaches and subsequent tools. Notations and languages that were previously designed by and for mathematicians are now adapted to the engineer's needs. The user interfaces are a major concern of most of the publicly available tools, especially the commercial ones. One step after the other formal verification methods have been adopted within the hardware community. Increasing cooperation between industry and formal methods researchers give rise to practical and even more efficient formal verification approaches.

Recent discoveries allow us to verify always larger designs with always more detailed properties. Complete formal verification of large complex systems

becomes practical at this time, and a great increase in confidence in the system can be obtained by the use of formal methods at key locations in the system.

We do not assert formal methods are the silver bullet<sup>1</sup> that can magically lay all our problems to rest, citing Frederick P. Brooks, Jr. [Bro86]. Formal methods are rather a complement to good design methodology and testing.

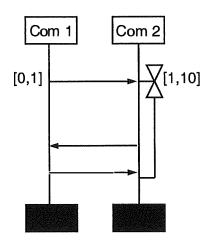

The techniques of *automated* verification developed widely for the past two decades, and we try make a contribution. Our work investigates how formal proofs can be done on designs under development, and we try to make a contribution by improving some steps of this complex process, focusing on the translation of the specification set to allow more efficient verification methods to be used.

#### Master thesis structure

In chapter 1 we present the formalism we use to describe the properties we want to verify, namely *Live Sequence Charts* (LSC) [DH98]. LSCs are used to describe the interactions between many components of a reactive system within one scenario. They provide a means to distinguish between mandatory and possible behaviors of the components. We translate these charts into timed automata, to enable the automatic verification of the specification. Therefore we introduce a timed automata formalism and describe the translation of LSCs into such automata.

Chapter 2 describes how the problem of formal verification can be reduced to the problem *model checking* [CGP99]. We therefore describe the most widely used logics and techniques to automatically verify properties. Other approaches than model checking are evoked, as the automata-theoretic approach, for instance. An overview of more recent techniques, which are currently used in the model-checking field, is given as well.

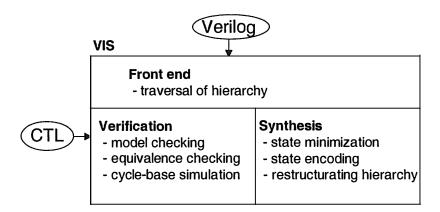

Chapter 3 can be seen as the application of the previous chapter. After a quick survey of some well-known verification tools we apply the previously cited formal verification techniques into a real environment. The VIS model-checker, developed at Berkeley and Boulder, is investigated into much more details. Finally a complete verification tool suite, i.e. Statemate, from I-Logix Inc., illustrates the whole verification process. These tools are parts of the verification environment of the Embedded System department of the Carl von Ossietzky Universität, Oldenburg.

Chapter 4 includes the most original part of our work. We define here a class of properties which can be verified more efficiently using invariant check [RS99], rather than model checking techniques. Therefore, we firstly characterize a class of properties represented by timed automata that can be verified using this invariant check. We extend algorithmically this class of properties, and define on the LSC level the properties one would be able to check on this improved way. Most of the properties one could want to verify in real (industrial) usage turn out to belong to this class.

Chapter 5 completes the translation chain our initial LSC specification has to undergo in order to be checked. We hence introduce a simple imperative

<sup>&</sup>lt;sup>1</sup>The one crafted to kill the werewolf of our nightmares.

formalism, SMI, which allows us to translate the automaton of chapter 1 into a finite state machine understandable by the VIS model checker. This translation allows us, it is worth to mention, to take advantage of the improved verification we described in the previous chapter.

Chapter 6 presents the improvements that were brought to our verification environment by the prototypical implementation of the verification tool chain we described.

### Chapter 1

# Specification basics

### 1.1 Introduction to specification

We use many different formalisms as they are all adequate for an aspect of the reality we want to describe, and the vocabulary of the physician is (hopefully) not the one of the mechanician. Besides their differences regarding their field of application, formalisms can also be distinguished with respect to their expressiveness. One will straightforwardly describe some music piece using scores, whereas the same music piece will be written in chords or tabulars to give more room for improvisation. From these different "vocabularies", let us call them *formalisms*, each fits well a different aspect of the same reality, the music piece.

Some formalisms are intuitive, some are not, but the latter could provide a more accurate description. It is obvious that the formalisms we use heavily depend on the habits of our environment. The example of native languages speaks for itself.

We will further use some well-known formalisms in the world of requirements engineering that fit our needs well, trying to describe them on both intuitive and formal way. They were chosen because of historical reasons, or after an in-depth survey of the available languages. The Symbolic Timing Diagrams (STDs) formalism belongs to the first category. It is used to describe the internal behavior of a component. Live Sequence Charts (LSCs) belong to the second, and are used to describe the interactions between many components into a reactive system. LSCs are described in section 1.2. Although STDs are not reviewed in this paper, one can refer to [FJ96] for a description of this formalism. Temporal Logics (described in section 2.2) can also be used to specify interesting properties of reactive systems.

As all these formalisms are used for the same purpose, to specify a requirement, we translate them all into a single formalism, the Timed Büchi Automata. This formalism is expressive and formal enough to allow to reason on it. We describe this intermediate formalism in section 1.3, and show how to translate the previously cited "high-level" specifications languages into one of our automata.

### 1.2 Live Sequence Charts (LSCs)

#### 1.2.1 The birth of LSCs

In the development of software as well as hardware systems, visual languages are becoming increasingly popular due to their graphical appeal. Especially the telecommunications domain has been using visual languages for many years. In this field the language of *Message Sequence Charts* (MSCs) became a popular means for specifying scenarios that capture information exchange in communication systems [IT96, AE01]. Such languages have been adopted to specify messages passing between components in other fields as well. One token of this expansion is the inclusion of an object-oriented variant of Message Sequence Charts, called Sequence Diagrams, in the UML standard [JRB99] used world-wide as reference formalism.

MCS's language is known to suffer a lack of expressiveness [HP98]. Neither does it provide the formal rigor which we feel is needed for sequence charts to be useful for formal utilization. This motivated the introduction of a sequence chart dialect which remedies these shortcomings: Live Sequence Charts (LSCs). LSCs were introduced by Werner Damm and David Harel in 1998, their major improvement with respect to MSCs and previous sequence charts is to provide a means to distinguish between mandatory and possible behaviors [DH98]. This is done by providing the ability to designate most LSC's elements as belonging to either the hot or the cold category, characterizing respectively the mandatory and provisional behaviors. This bi-modal property is called the temperature of an object.

The next sections present the key elements of Live Sequence Charts (LSCs) following the approach of [DH98]. We introduce some of the extensions to this formalism made by its authors in 2001, and some particular features which were first described in [KW01].

#### 1.2.2 Formalism description

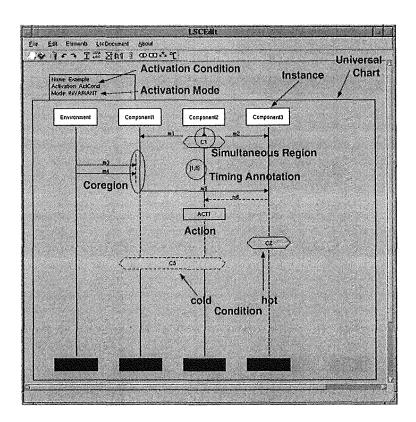

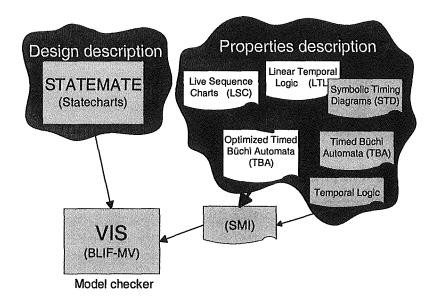

The formalism of LSCs, as appeared in [DH98], provides a rich set of features to describe scenarios, from which we will consider a few, focusing on the core concepts. The graphical representation of this language contributes largely to the easy understanding of LSCs specifications, hence we will illustrate many of the concepts within the LSC shown in figure 1.1 on page 13.

The basic idea of LSCs, as we already told, is to allow a distinction between *mandatory* and *possible* behaviors. To do so, most objects used in the language must be declared to belong to one of those two exclusive modes. Graphically speaking, mandatory, called *hot* elements, are depicted in solid lines, and possible ones (*cold*) in dashed lines.

#### 1.2.3 Constructs of the language

#### Instances

Each instance represents one participant to the scenario the LSC describes. Instances are represented by vertical lines along which the time runs, from top

to bottom. The environment is often depicted as an instance, rather than the border of the LSC, like in the MSC formalism. This allows more flexibility regarding the environment, allowing for instance to specify assumptions on its behavior as for any other instance.

We do distinguish between environment and regular (component) instances. A violation of a LSC which result from a wrong behavior of the environment need to be treated differently than those caused by the system. In the former case we exit the LSC without an error and in the latter case consider it as a real specification violation.

There are four instances in our example LSC on page 13, three are components and the latter is the environment.

#### Locations

Many locations are linked each to one *event* on an instance. An event related with a location occurs *before* any event related with a *lower* location on same instance. This *chronological order* is relevant on a single instance only, we cannot compare occurrence time of locations on different instances on their relative (graphical) position. The first location of an instance is called *initial* and the last *maximal*.

#### Messages

Messages are sent between the instances. Their sending or receiving are called events. As the emission of a message must occur before its reception, we can deduce some ordering information between locations on different instances.

We consider two kinds of messages: asynchronous and instantaneous ones, while  $[\mathrm{DH98}]$  distinguished between synchronous and asynchronous communication.

An *instantaneous* message means that the sending event and receiving event happen at the same time. A *synchronous* message means that the sender is blocked until the receiver has completed whatever request the sender has made. Only the sender and receiver are concerned with this *blocking issue*, the other instances may proceed along their own execution thread. Synchronous communication thus entails a notification of its completion. In a LSCs we require the user to make the return message explicit to highlight the fact that such a process consumes time, and to make the formalism more intuitive. *Asynchronous* messages can take a certain time to get from the sender to the receiver, and do not impose the sender to wait for its arrival, like posting a letter. One could simulate the asynchronous message mechanism using many synchronous messages that transit through a "channel" instance.

Messages are represented by arrows, going from the location associated with their emission event, to the location where they are received. Asynchronous messages have an open-ended arrow, instantaneous ones a solid head. Asynchronous messages are to be drawn slanted as time passes while they are on their way. Instantaneous messages are drawn horizontally, showing the simultaneity of their emission and reception. All messages shown in figure 1.1 on page 13 are instantaneous ones.

#### Temperature

The temperature concept applies to many objects, indicating how to progress along the instances and messages. Labelling a location with the *hot* temperature (solid line draw) involves the chart *must* progress beyond this location. The analogy is that one can not remain forever in a hot location without burning one's feet. The maximal locations must be cold since we cannot oblige an instance to go further after reaching its last location.

Temperature applies to most of the concepts of LSCs including the entire chart, hot charts are called *universal charts* and cold one *existential charts*. We do not consider the existential charts for the moment as they are not handled by the translation algorithm we use [KW01]. Furthermore the universal interpretation seems to be the natural choice for formal specification, focusing on the fact that an entire system fulfills the specification. The graphical distinction between both is shown in the box surrounding the LSC, which is thus dashed for existential and solid for universal charts.

Combining locations, messages and temperature allows us to express all possible communication behaviors in table 1.1.

| temperature | hot                                | cold                   |

|-------------|------------------------------------|------------------------|

| locations   | instance run must move             | instance run may stay  |

|             | beyond location                    | infinitely at location |

| message     | message will be received once sent | message may be lost    |

Table 1.1: Temperatures for locations and messages

#### **Conditions**

Statements about the system state can be expressed using conditions. Conditions are boolean expressions referring to attributes or data items of the involved components (instances), evaluated when all instances concerned reach the location corresponding to the condition entry. They are graphically represented by an elongated hexagon. Instances which are involved in the condition have their instance axis interrupted by the condition, whereas instances axis of components not participating in the condition continue through the condition. In the example LSC components 1 and 2 are involved in condition C2, whereas the environment and component 3 are not, see page 13.

Conditions can be hot or cold. Hot conditions have to hold unless the scenario fails. Cold ones should be met for the scenario to be validated, but expresses, when violated, that we are not considering a scenario we wanted to talk about, thus exiting without errors. This semantics is not conform to the definition of temperature of [DH98], as it is used here to describe liveness rather than progress, but it allows interesting specification when combined with subcharts, like conditional behaviors or iterations. We won't detail cold locations nor sub-charts, as they are out of our current focus, but one can refer to [DH98] for more details.

#### Coregions and simultaneous regions

The chronological order between events is induced by the sequence of locations on one instance, messages and conditions ranging over more than one instance, that can be viewed as synchronization points.

There are two possibilities to change the ordering along the instance axis, should this total order be too restrictive: simultaneous regions and coregions.

To have unordered locations of the same instance, one can put them into a coregion. Coregions are drawn by a dashed vertical line, parallel to the whole concerned instance portion. Within a coregion all events become unordered, as for the arrivals of messages m3 and m4 on page 13.

A simultaneous region states that all events contained in this region must happen at the same time. This feature has been added to the initial LSC formalism in 2001. It allows to specify the simultaneous observation of several events, as one can meet in the STATEMATE environment described in section 3.3. Such a region is graphically expressed through many events occurring on the same instance at the same height (time), like messages emissions and synchronization through a condition. Before this construct was added to the formalism, a LSC scenario could only describe pure interleaved behaviors, where one instance was allowed to progress at a time. Simultaneous regions make the formalism really adapted to describe parallel execution of communicating devices. Simultaneous regions may not appear in coregions, because otherwise they would imply an order (of simultaneity) to some events of the coregion.

#### Actions

Actions represent internal behavior of an instance and consequently no impact of an action is observable. They are represented by a rectangle, the border of which depends on the action temperature. Actions are treated as mere comments, we won't consider them in the remainder of this report.

#### Activation conditions and modes

The range of the specification is described by an activation mode. Three different modes, initial, invariant and iterative, allow us to tell whether the scenario should hold for ever, or only once. A mode is coupled with an activation condition, ranging over the state of the systems, i.e. the instances and the environment. Activation modes are explained in section 1.5, let's just say the iterative mode does not belong (yet?) to the LSC formalism of [DH98].

Both activation mode (A.M.) and activation condition (A.C.) are simply written above the upper-left corner of the chart. As it can be seen, the LSC in figure 1.1 is an INVARIANT scenario that will thus be activated every time ActCond is evaluated to true.

#### Timer, timing annotations

To be able to express properties about real-time systems, as vital as toasters or airplanes autopilot robots, we use timing annotations and timers. Timing annotations depict the (finite) interval of time for a location to be traversed.

They are written using the mathematical notation for an interval besides the concerned location. For instance, in the example LSC on page 13 the possible arrival of message m6 should occur at least one time unit, and at last five time units after component2 left the condition C1.

Timing annotation can be added only to hot locations. Such an annotated location has then to be traversed within the interval.

Timers can be viewed as timing annotations ranging over more than two successive locations of an instance. A timer is represented sometimes by an hourglass with the wanted time values, sometimes only by the time values, with a line going to the location corresponding to the initialization of the timer, and another line going to the location where it runs out. Both locations are located on the same instance.

#### Sub-charts

We allow a single use of sub-charts, i.e. LSCs without activation information which are integrated into a main one, as IF-THEN-ELSE construction. Such a sub-chart is characterized by a single condition and two integrated subcharts, the first of which is activated if the condition holds, otherwise the second one is. This construct differs from the sub-charts of [DH98] inasmuch as different conditions were used in the initial formalism, evaluated at different time, hence allowing both sub-charts to be traversed by the same run of the system. This later behavior seems far from the conduct that one could expect from a real alternative. We thus redefined this construct to fit our needs.

#### 1.2.4 LSC interpretation

We explained how most of the elements of Live Sequence Charts are to be interpreted, at least intuitively, in the previous section. We will now sketch a more formal formalism, i.e. timed automata (1.3), to allow us to describe how the LSC specifications can be translated into these automata (1.4). In the next chapters we describe how these timed automata can be used for formal verification of the initial (LSC) specification. For a more complete syntax and semantics of LSCs the reader could refer to [DH98].

Some restrictions are put in order to simplify the interpretation of LSCs. We do not allow any other element parallel to and independent of a sub-chart. To ensure this we require the sub-chart to cover all instances of the LSC. The second restriction involves the setting of a timer, which has to be bound (via a simultaneous region) to some sort of event. This is adapted to the intuition of a timer, which is set when some event is observed, and then counts time until a subsequent event occurs.

We already made some remarks on the combinations of features: one cannot include a simultaneous region within a coregion, since this would imply an ordering (of simultaneity) on some events of the coregion. The same way we don't allow many conditions to appear in the same coregion, nevertheless many conditions can always be merged in a single one.

Figure 1.1: LSC example

### 1.3 Automata theory on infinite words

LSCs describe the communication behavior of reactive systems. Such systems interact with their environment during their all execution, which is often infinite. We want to translate every specification languages used into a single formalism, as stated in 1.1, which should hence accept infinite words, because of the possible endless execution of the system. There exist several different automata which satisfy this requirement. For our purposes Büchi automata on infinite words are sufficient. We introduce them in the remainder of this chapter. In order to be able to treat time aspects, we extend them to timed Büchi automata (TBAs) and finally show how LSCs can be translated into these TBAs.

#### 1.3.1 Finite automata on infinite words

Formal languages are typically characterized as a set of finite words formulated over a finite alphabet [HU77] as are traditional computing languages or human languages, for instance. Such words can be recognized by finite automata and can also be characterized by mathematical regular expressions. The expression  $a^*(a|b)$  for instance, describes the finite set of all words beginning with a finite sequence of a's, followed by a single a or a single b.

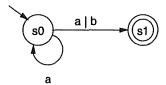

An automaton is simply a mathematical model of a device that has a constant amount of memory, independent of the size of its input [CGP99]. An automaton on *finite words* can be represented as a graph with labelled transitions, in which the set of nodes are the different possible states of the system and the edges are given by all evolutions possible from any state. Some of the states can be accepting, meaning the system could acceptably stay forever into one of those, without any further evolution. The automaton on finite words in figure 1.2 defines exactly the same language as the regular expression a \* (a|b).

Figure 1.2: The automaton on finite words that accepts  $a^*(a|b)$

Languages of *infinite words* can be similarly recognized by finite automata on infinite words, called  $\omega$ -automata, and are also expressible as  $\omega$ -regular expressions. The expression  $a^*(a|b)^{\omega}$  for instance, describes the finite set of all words beginning with a finite sequence of a's, followed by an infinite sequence of a and b.

Many different types of finite automata on infinite words have different acceptance conditions, such as Büchi automata, Muller automata or Rabin automata. The reader could refer to [Tho90] or [AD94] for a survey. We will only discuss Büchi 's automata in this report as they are sufficient for our purposes.

#### Nondeterminism

The automaton of figure 1.2 illustrates a major concern of the automata formalism: when being in state  $s_0$  and next input symbol is a a, should we remain in state  $s_0$  or go to  $s_1$ , as both are possible according to the transition label.

This possible choice is called *nondeterminism* and simply means that such nondeterministic automata can have multiple same labels on the outgoing transitions of a same state.

Any nondeterministic automaton on finite words can be translated into a deterministic one that accepts the same language" [CGP99], while this is not the case for Büchi automata.

#### Formal definition

Formally a (non-deterministic) Büchi automaton (on infinite words)  ${\mathcal A}$  is a tuple

$$\mathcal{A} = (\Sigma, S, S_0, \longrightarrow, F)$$

, where

- $\Sigma$  is the finite *alphabet*.

- S is the finite set of states.

- $\longrightarrow \subseteq S \times \Sigma \times S$  is the transition relation.

- $S_0 \subseteq S$  is the set of *initial states*.

- $F \subseteq S$  is the set of accepting states.

A transition  $(s, \sigma_i, s') \in ---$  represents the change from state s to state s' on input symbol  $\sigma_i$ . We typically write a transition in the form  $s \xrightarrow{\sigma_i} s'$ .

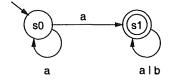

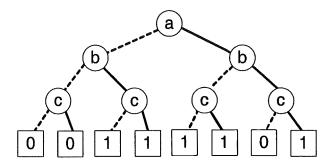

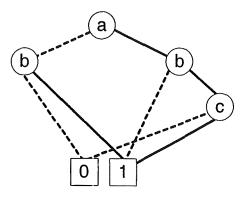

As we told, an automaton can be represented as a graph with labelled transitions, its set of nodes is S and the edges are given by ---. In the example shown in figure 1.3 we can find that  $\Sigma = \{a, b\}$ ,  $S = \{s_0, s_1\}$ ,  $S_0 = \{s_0\}$  and  $F = \{s_1\}$ . Initial states are shown with an incoming array whereas accepting states are double circled.

Figure 1.3: The automaton on infinite words that accepts  $a^*(a|b)^{\omega}$

Let  $\sigma=\sigma_0\ \sigma_1\dots$  be an infinite word over the alphabet  $\Sigma$ . A  $run\ \rho$  of the automaton  $\mathcal A$  over this word  $\sigma$  is defined as a sequence of states:  $\rho=s_0\ s_1\ \dots$ , such that

- $s_0$  is an initial state:  $s_0 \in S_0$ .

- the target state of each transition is the source state of the following transition:  $\forall i \geq 0 : (s_i, \sigma_i, s_{i+1}) \in ----$ , where many transitions going out from the same state can be labelled by the same character, as the automaton is nondeterministic.

The run  $\rho$  over  $\sigma$  can also be written  $\rho: s_0 \xrightarrow{\sigma_0} s_1 \xrightarrow{\sigma_1} \dots$

A run  $\rho$  of  $\mathcal{A}$  over  $\sigma$  is accepting if some accepting state appears infinitely often in  $\rho$ . This criterion is called Büchi acceptance criterion.

Formally the Büchi acceptance criterion states that those runs are accepted by a Büchi automaton  $\mathcal{A} = \langle \Sigma, S, S_0, \longrightarrow, F \rangle$ , which visit some state  $s \in F$  infinitely often. Let  $inf(\rho) := \{s \in S \mid \forall \ i: \ s = s_i \in \rho : \exists \ j > i: s = s_j \in \rho\}$  denote the set of states which are visited infinitely often by a run  $\rho$ . A word  $\sigma = \sigma_0 \ \sigma_1 \dots$  is then accepted by  $\mathcal{A}$  iff there is a run  $\rho$  over  $\sigma$  such that  $inf(\rho) \cap F \neq \emptyset$ . Such a run is called an accepting run.

Let  $\Sigma^{\omega}$  be the set of all infinite words over  $\Sigma$ , the language  $L(\mathcal{A})$  accepted by  $\mathcal{A}$  as expected consists of those words  $\sigma \in \Sigma^{\omega}$ , for which there is an accepting run, i.e.  $L(\mathcal{A}) := \{ \sigma \in \Sigma^{\omega} \mid \exists \ \rho : s_0 \xrightarrow{\sigma_0} s_1 \xrightarrow{\sigma_1} \ldots : inf(\rho) \cap F \neq \emptyset \}.$

The language accepted by a Büchi automaton can also be characterized by an  $\omega$ -regular expression. A language is called  $\omega$ -regular iff it is accepted by some Büchi automaton. The automaton shown in figure 1.3 accepts the language  $a^*(a|b)^{\omega}$ , where  $\omega$  indicates infinite repetition.

#### 1.3.2 Timed finite automata on infinite words

Until now our automata allow us to express properties concerning the sequencing of events (states) of a system. (Un)fortunately many crucial systems depend on real-time considerations, remember the toaster, and not only on their qualitative sequence. Rajeev Alur and David Dill [AD94, Alu97] developed a theory on timed finite automata on continuous time model. We recall some of their intuition, but rather develop a discrete time framework, since such a context is more intuitive to the system designer and easier to check formally. Follow the way of [AD94] we associate an occurrence time to each symbol of a word, yielding timed words.

#### Intuitive timing

In the untimed case the behavior of an automaton depends only on the input symbols, i.e., being in some state, the next state(s) of an automaton is (are) determined by the current input symbol. In order for an automaton to accept timed words it needs a means to count time, since the choice of the next state(s) should also depend on the occurrence time of input symbols. Time is introduced into an automaton by adding a finite set of clocks. Time passes only when a transition is taken<sup>1</sup>. A clock can be reset to 0 along any transition and at any time the reading of a clock corresponds to the time elapsed since its last reset. With each transition we associate clock constraints, and require the current clock values to satisfy this constraint for the transition to be enabled. With each state we associate a clock constraint called its invariant or stable condition, and require the time can elapse within a state, i.e., clock values can increase, as long as its stable condition is satisfied. In that way we force the input word to conform to certain timing requirements.

<sup>&</sup>lt;sup>1</sup>in this way we distinguish from the timed automata of [AD94] where transitions take no time and time only passes within a state

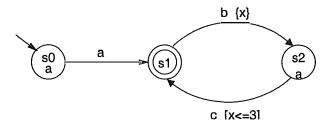

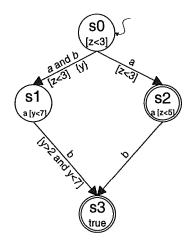

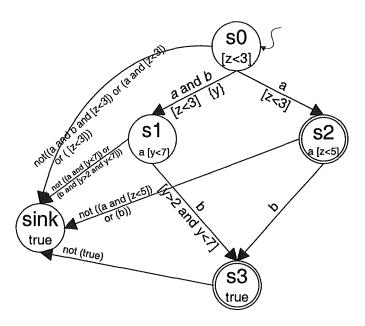

Figure 1.4 shows an example of a timed Büchi automaton  $\mathcal{B}$  which has an alphabet  $\Sigma = \{a, b, c\}$ , a set of states  $S = \{s_0, s_1, s_2\}$ , a single initial state  $S_0 = \{s_0\}$ , a single clock  $C = \{x\}$ , a single accepting state  $F = \{s_1\}$ , and whose transition relation  $\longrightarrow$  and stable conditions are drawn.

Figure 1.4: timed automaton example

#### Time interpretation

Time is represented by a sequence of time values which has to satisfy two intuitive constraints: time only advances and time never stands still. More formally, a *time sequence*  $\tau = \tau_0, \tau_1, \tau_2, \ldots$  is an infinite sequence of time values  $\tau_i \in \mathbb{N}$  the set of positive integers, for which the following holds:

- 1. We begin the observation at first available instant:  $\tau_0 = 0$

- 2. Time is strictly increasing:  $\forall i \geq 0 : \tau_i < \tau_{i+1}$

- 3. Time is infinite:  $\forall t \in \mathbb{N}: \exists i > 0: \tau_i > t$

A timed word over an alphabet  $\Sigma$  is then defined as a pair  $(\sigma, \tau)$ , where  $\sigma = \sigma_0 \ \sigma_1 \dots$  is an infinite word and  $\tau = \tau_0 \ \tau_1 \dots$  is a time sequence. The time value  $\tau_i$  denotes the occurrence time of input symbol  $\sigma_i$ .

Before giving the formal definition of a timed automaton it is necessary to explain what type of clock constraints are allowed as stable conditions and enabling conditions, and how the value of any clock is determined. For our purposes it is sufficient to allow comparison of clock values to constants and conjunctions, even if [AD94] used many more constructors within their clock constraints. Any value of  $\mathbb N$  can be used as a time constant. The formal definition of the set  $\Phi(C)$  of clock constraints  $\gamma$  over the set C of clock variables is defined by the grammar:

$$\gamma := x \le c \mid x \ge c \mid \gamma_1 \land \gamma_2$$

where x is a clock in C and c is a constant in  $\mathbb{R}^+$ .

In order to evaluate the clocks a *clock interpretation* is needed. A clock interpretation  $\nu$  assigns to each clock  $x \in C$  a value of the time domain. Formally a clock interpretation is a mapping  $\nu: C \longrightarrow \mathbb{N}$ . Let I be the set of all clock interpretations. The truth value of a clock constraint  $\gamma$  is then given by substituting all clocks in  $\gamma$  by their interpretation:

$$\llbracket . \rrbracket : \Phi(C) \times I \longrightarrow \mathbb{B}$$

$$\llbracket x \le c \rrbracket(\nu) := \nu(x) \le c$$

$$\llbracket x \ge c \rrbracket(\nu) := \nu(x) \ge c$$

We say that a clock interpretation  $\nu$  for C satisfies a clock constraint  $\gamma$  over C iff  $\gamma$  evaluates to **true** according to the values given by  $\nu$ . Regarding the timed automaton of figure 1.4, we can see a clock interpretation  $\nu$  that assigns 2 to x would satisfy the clock constraint  $x \leq 3$  on transition from  $s_2$  to  $s_1$ .

$[\![\gamma_1 \land \gamma_2]\!](\nu) := [\![\gamma_1]\!](\nu) \land [\![\gamma_2]\!](\nu)$

We write  $\nu + t$  the clock interpretation which maps every clock x to the value  $\nu(x) + t$ , and we write  $\nu[Y := 0]$  the clock interpretation which assigns 0 to each  $x \in Y \subseteq X$ , and agrees with  $\nu$  over the rest of the clocks in X.

We define these timed automaton more formally in the next section.

#### 1.3.3 Timed Büchi automaton

Our Büchi automaton use a more concise labelling notation than the one used for untimed automaton. Rather than having a distinct transition labelled with each character a of the alphabet  $\Sigma = 2^{AP2}$ , the labels consist of boolean formulas over the atomic propositions of AP. One can compare this comprehensive notation to the one used for the clock predicates  $\Phi(C)$ . We show easily that this simplified representation is equivalent in expressiveness to the extended one simply by giving a mapping from any boolean formula that appears in our TBA to a single character, and define the set of these character as the alphabet of our automaton. Formally we denote by  $\mathbb{B}(AP)$  the set of boolean formulas over the atomic propositions AP.

Formally a (nondeterministic) timed Büchi automaton A is then a tuple

$$\mathcal{A} := \langle AP, S, s_0, C, \longrightarrow, F, SC \rangle$$

, where

- AP is a finite set of atomic propositions

- $\bullet$  S is a finite set of states.

- $s_0 \in S$  is the single initial state.

- C is a finite set of clocks.

- $F \subseteq S$  is a finite set of accepting states.

- SC: S → B(AP) × Φ(C) is a function that maps each state to its stable condition, ranging over the predicates on atomic propositions and clock constraints.

A stable condition  $SC(s) = (b_s, \gamma_s)$  states that the automate is allowed to remain in state s as long as both the predicate  $b_s$  and the clock constraint  $\gamma_s$  are satisfied.

<sup>&</sup>lt;sup>2</sup>which notation is also used by [AD94]

•  $\longrightarrow \subseteq S \times \mathbb{B}(AP) \times 2^C \times \Phi(C) \times S$  is the transition relation with labels given by the more concise formulas (rather than individual characters from  $\Sigma = 2^{AP}$ ).

A transition  $(s_i, b_i, r_i, \gamma_i, s_{i+1}) \in \longrightarrow$  represents the change from state  $s_i$  to state  $s_{i+1}$  with  $b_i$  satisfied. The set  $r_i \subseteq C$  indicates which clocks are reset when taking the transition and  $\gamma_i$  is a clock constraint that specifies when the transition is enabled, this constraint is evaluated before the clock resets.

In the automaton of figure 1.4 the transitions are simply labelled by the predicate on the alphabet, the clocks to be reset are indicated within braces and the clock constraint is written between brackets.

#### Semantics

When dealing with timed automata the runs which are considered have to reflect time as well. A timed run tr of a timed automaton  $\mathcal{A}$  over a timed word  $(\sigma,\tau)$  is an infinite sequence of pairs  $(s_0,\nu_0)$   $(s_1,\nu_1)\ldots$  where  $s_i\in S$  is the *i*-th state visited by the automaton and  $\nu_i\in I$  is the clock interpretation in this state, we write

$$tr: (s_0, \nu_0) \xrightarrow[\tau_0]{\sigma_0} (s_1, \nu_1) \xrightarrow[\tau_1]{\sigma_1} (s_2, \nu_2) \xrightarrow[\tau_2]{\sigma_2} \dots, \text{with}$$

- $\forall i > 0 : s_i \in S, \nu_i \in I$ .

- $s_0 \in S_0$ .

- $\forall x \in C : \nu_0(x) = 0$ , all clocks are initialized to zero.

- $\forall i \geq 0$  either  $\exists (s_i, b_i, r_i, \gamma_i, s_{i+1}) \in \longrightarrow : \llbracket b_i \rrbracket (\sigma_i) = \text{true} \text{ and } \llbracket \gamma_i \rrbracket (\nu_i) = \text{true} \text{ and } \nu_{i+1} = (\nu_i + \tau_i) \llbracket r_i := 0 \rrbracket$  or  $s_i = s_{i+1}$  and, if we call  $SC(s_i) = (b_i, \gamma_i)$  we have  $\llbracket b_i \rrbracket (\sigma_i) = \text{true}$  and  $\llbracket \gamma_i \rrbracket (\nu_i) = \text{true}$  and  $\nu_{i+1} = (\nu_i + \tau_i)$

The taken transition or stable condition respects its atomic proposition and clock predicates, resets all appropriate clocks and the next clock interpretation is coherent with elapsed time.

To define the run we used the same "interpretation" notation for the formulas on atomic propositions than the one we defined for clocks, except the context of interpretation is here given by the considered input.

The question of which (timed) runs are accepting ones leads to the definition of acceptance criteria for timed automata. We do this analogously to the untimed version, using the same acceptance criteria for automata on infinite words which can be applied to both the timed and the untimed versions.

Again we only consider Büchi acceptance here, for other definitions of acceptance criteria see [AD94]. Timed Büchi automata combine Büchi acceptance with timed automata intuitively described above. As for the untimed case we define the set inf(tr) of states of a timed run, which are visited infinitely often:

$$inf(tr) := \{ s \in S \mid \forall i \text{ with } s = s_i, (s_i, \nu_i) \in tr : \exists j > i : s = s_j, (s_i, \nu_i) \in tr \}.$$

A timed word  $(\sigma, \tau) = (\sigma_0, \tau_0) (\sigma_1, \tau_1) \dots$  is then accepted by  $\mathcal{A}$  iff  $\inf(tr) \cap F \neq \emptyset$  holds for the corresponding timed run tr. The language accepted by a timed Büchi automaton is correspondingly defined as

$$L(\mathcal{A}) := \{ (\sigma, \tau) \in \Sigma^{\omega} \times \mathbb{N}^{\omega} \mid \exists \ tr = (s_0, \nu_0) \xrightarrow[\tau_0]{\sigma_0} (s_1, \nu_1) \xrightarrow[\tau_1]{\sigma_1} \ldots : inf(tr) \cap F \neq \emptyset \}.$$

As an example the automaton  $\mathcal{B}$  in figure 1.4 accepts the language  $a^*(ba^*c)^{\omega}$  restricted to the words in which a c occurs before the 4-th time unit after a b occurred:

$$L(\mathcal{B}) = \{ (\sigma, \tau) \mid \sigma \in a^*(ba^*c)^{\omega} \land \forall i \ \exists j > i : \sigma_i = b \implies \sigma_j = c \land \tau_j \leq \tau_i + 3 \}.$$

#### Additional definitions

We finally define an activated TBA as a tuple  $\langle mode, actCond(A), A \rangle$  where mode is either initial, invariant or iterative, actCond(A) is the activation condition activating A and A is the so-called main automaton, a TBA. Note that the activation condition could be expressed as an automaton.

By convention we can use A to designate both the TBA and the activated TBA, as it is clear from the context which we are talking about.

We finally define a TBA specification as a finite set of activated TBAs:  $TBA_{spec} = \{A_1, A_2, \dots, A_k\}$

#### Semantical remarks

The transition relation  $\longrightarrow$  does not include self-loops, thus for all  $i \ge 0$  such that  $(s_i, b_i, r_i, \gamma_i, s_{i+1}) \in \longrightarrow$  we have  $s_i \ne s_{i+1}$  (destination node is different from source node).

More practical restrictions are brought to this formalism at the end of the chapter, resulting in a more efficient language. These restrictions are motivated by the particular result of the translation of specifications into TBA, therefore we detail first this translation, called unwinding, in section 1.4, and give more details in section 1.6 about the TBA formalism which has been described here.

### 1.4 Unwinding LSCs into TBAs

The translation of a Live Sequence Chart (LSC) into a Timed Büchi Automaton (TBA) is called *unwinding*, as we will see the LSC form is (a bit) more compact. The algorithm we explain here has been first described by Jochen Klose and Hartmut Wittke in [KW01], and is based on the procedure of [FJ96] to unwind Symbolic Timing Diagrams.

#### 1.4.1 Intuitive procedure

The purpose of the unwinding procedure is to, finally, get a timed automaton in which each (reachable) state represents one possible state of the LSC, having all the possible states of the LSC included into the automaton. Both the TBA and the LSC should specify the same behaviors, of course.

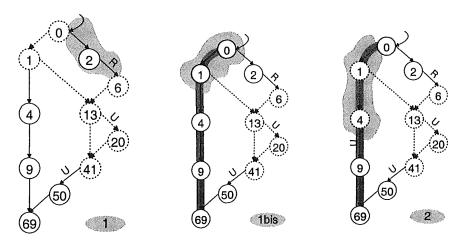

The possible "states" of a LSC are called *cuts*, they can be viewed as a (curve) line through the chart, across (cutting) all the instances, meeting exactly one location of each of them. Two special cuts are defined, one including all the initial locations, the other all maximal locations. The unwound corresponding states are the (only) initial state and an accepting state of the automaton, labelled by a true stable condition since we are allowed to stay forever in this state.

We begin the unwinding procedure with the initial state, at the top of the chart, and let a "front" down, accordingly to the meaning of each object encountered, every event crossed implies to create a new state in the automaton. We let the cut go downwards until we reach the maximal location on all instances, which state we declare to be acceptant.

#### 1.4.2 Pitfalls to the intuition

The application of this intuitive idea could be straightforward implemented, but we will first clearly define some more critical concepts of the LSCs, such as coregions, simultaneous regions and IF-THEN-ELSE sub-charts. This is done in the next section. The figure 1.5 shows a simple LSC on the left side, with all possible cuts drawn. We can see one critical position is the coregion on component C2, where Msg3 and Msg4 are received: many cuts go through this position, none should be forgotten by the unwinding procedure!

#### More formally

We establish a total order on all interesting events of a single instance axis: sending a message, receiving a message, the valuation of a condition, setting a timer, expiration of a timer or the reset of a timer, considering timing annotations are associated to timers. This total order is based on the graphical position of the event [KW01], let's call it position: Events  $\rightarrow$  Position.

All events belonging to the same simultaneous region have the same position, as well as events from the same coregion. The positions of these regions are defined as well, thus extending the definition of  $position : Region \rightarrow Position$ , where Region denotes the set of all the interesting place to characterize a LSC:  $Region = \{Events, Simultaneous regions, Coregions, Initials locations, Maximal locations\}.$

We can define the set of *strict predecessors* of a region using this total order along a single instance axis. This set is empty if r is an initial location, and is the set of direct predecessors of r otherwise. Usually predecessors(r) will contain a single event, except if a coregion or a simultaneous region is the strict predecessor of r.

Shared conditions and instantaneous messages force some regions to be simultaneous on different instances. We say these regions belongs to the same *simultaneity class*.

Using the simultaneity classes and the predecessor relation we are able to define the set of *prerequisites* of any region r, the set of regions of the LSC that must be traversed before r can be traversed. prerequisites(r) is obviously empty if r is an initial location, otherwise prerequisites(r) is the set of regions

Figure 1.5: Cuts of the unwinding procedure

which are the predecessor of any regions belonging to the simultaneity class of r.

With this definition we are able to formally unwind a LSC by first constructing the simultaneity classes, and then unwinding the regions in such an order their prerequisites have all been unwound before they are. The translations of the resulting automaton corresponds to the successor relation for cuts, i.e the message events that must be fulfilled to get to the next cut.

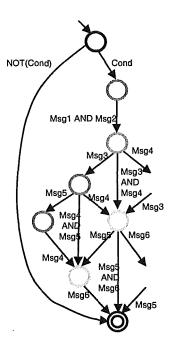

The unwinding structure obtained from the application of this procedure to the LSC of figure 1.5 is illustrated in figure 1.6

Figure 1.6: Unwinding structure

#### Considering timing

The depicted unwinding structure cannot express time, we will thus transform it into a Timed Büchi Automaton (TBA). This formalism, described in section 1.3.2, handles timing through clocks, that can be reset and used in *clock constraints*, either on the transitions labels or within the invariants of the states.

As we told in section 1.2.3, timing annotations can only be added to hot locations. They specify an interval of time [n,m], with  $n \leq m$ , both positive integers. This interval means that the annotated location has to be traversed (left) at least n and at most m steps after is has been reached. Let us imagine a hot location l on instance i is annotated with the time interval [1,4]. This means that when a run reaches l on i, l should remain the active location of i for at least one step, i.e. one clock increment, since we consider discrete time.

Furthermore l has to be left at most at the fourth step since it has been activate, otherwise the run is rejected and an error is generated.

To add this timing information to the unwinding structure we simply consider every hot locations as constrained by a (different) timer (clock). The corresponding timer is reset when the location is reached and a boolean expression constrains the clock value to be within legal range when it is traversed. This boolean expression is simply **true** if there was no timing annotation to this location, otherwise it recalls the timing.

The resulting TBA has *self-loops* on each state, labelled with the condition which has to hold for the TBA to stay in the associated state. These loops are needed since, in our formalism, time only passes when transitions are taken, they are what we called *stable conditions* in the TBA dialect (see section 1.3.2). Its transitions are the conjunction of the predicate from the unwinding structure and adding timing constraints.

#### Determinism in the TBA

The activation modes will be considered later, for the moment it remains as a comment, added to the TBA. A more worrying topic concerns the question of the determinism in the TBA, as it is directly related to the interpretation we give to the LSC's elements.

Three different options can be considered regarding the determinism of the unwound automaton, which depends on the labels we give to the self-loops of each state.

We could completely omit any information provided by timing annotations, providing a totally nondeterministic automaton, which is not efficient for verification purposes. A *strict* interpretation, as considered by [DH98], means that each occurrence of a message has to be explicitly noted in the LSC, and no other is allowed. This interpretation may be too strong, as we do not care whether visible messages are emitted at any time, as long as the desired scenario is fulfilled. The third interpretation, called *weak*, forces the TBA to react to the first occurrence of the expected message, but doesn't restrain the same occurrence at any other time. In a word, unexpected events are ignored. To achieve this mode, self-loops are labelled with the negation of the next message(s) of considered state.

#### An example

A simplification of the TBA produced by adding the timing consideration to the unwinding structure of figure 1.6 is shown in figure 1.7, with the modifications in bold. This one is a simplification inasmuch as states were put together to allow a better readability.

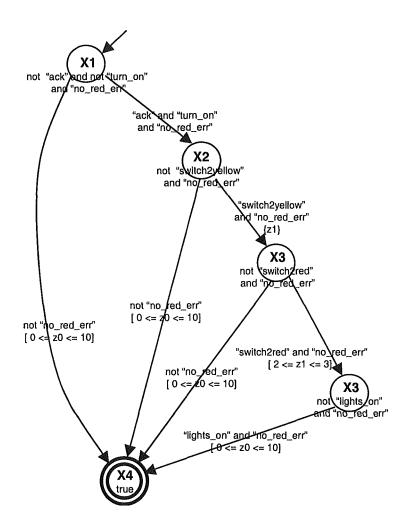

In appendix A we show a small LSC extracted from the specification related to a light-control system used for train rails. The TBA obtained by application of the unwinding procedure of [KW01] is provided as well.

Figure 1.7: TBA resulting from the unwinding procedure

#### 1.5 Activation modes

When describing properties we would like a system to have, it is obvious we also want to tell about the range of this specification: if it holds for ever or only once, for instance. This opportunity is given by adding an *activation mode* to a specification, paired with an activation condition.

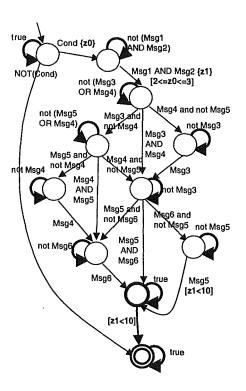

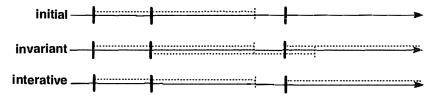

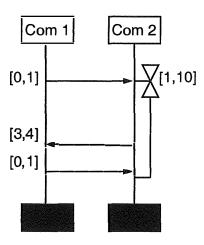

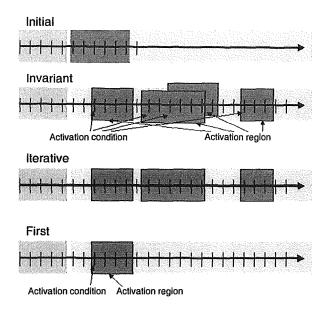

Two activation modes are used by [DH98] for the activation of a LSC: *initial* and *invariant*. We add the *iterative* activation mode. These three modes are illustrated in figure 1.8. The horizontal lines symbolize the time, running from left to right, each vertical mark represents an occurrence of the activation condition, which results or not in an activation of the specification, i.e. the verification of the scenario, (in dotted line) according to the activation mode.

Figure 1.8: Three activation modes

We describe the three activation modes within the next sections and compare their use within both LTL formulas (see 2.2.1) and finite automata (see 1.3.1). Nevertheless the activation mode remain as a comment to the specification, either in LSC or TBA format, we really integrate it into the specification only in a further step of the process, at the SMI level, as explained in section 5.5.2.

#### 1.5.1 Initial mode

The *initial* mode activates the specification immediately, i.e at the first step of the run, the *activation condition* has to hold and the run to be fair to be accepted.

The specification is also accepted if the activation condition does not hold at first step while the *activation exception* does. In this case the specification is not activated, and the run immediately succeeds. If the activation condition is not satisfied at the first step and neither the activation exception, then the run is rejected.

Such a behavior is easily implementable with LTL formulas. If we write act the activation condition and P the property coded by the LSC, we can represent the initial mode by the LTL formulae  $(act \land \bigcirc P) \lor (\neg act \land exception)$ .

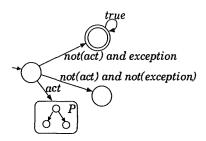

The check of the same condition with a finite automaton is straightforward and results in the automaton which can be seen in figure 1.9.

#### 1.5.2 Invariant mode

In the invariant mode the input sequence is checked any time the activation is evaluated to true.

Figure 1.9: Automaton in initial mode

The LTL formula for such an activation mode is of the form  $\square$  (act  $\Longrightarrow$   $\bigcirc$  P).

The invariant mode cannot be represented graphically, as we should duplicate all the P evaluation automaton as many time as needed. It is possible to build a product-automaton (see section 2.3.2), but this is hard while handling many clocks. Since our automata are complementable one could also check the formula  $\neg \diamondsuit (act \land \bigcirc \neg P) \implies act \land \bigcirc \overline{P}$ , but the double complement can be expensive, as stated in [BH]. Finally we could also handle this mode by nondeterministically activate the verification of the specification each time the activation occurs.

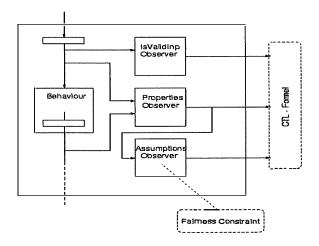

Nevertheless we should check only the activations which are able to lead to some problems, as shown in figure 1.10, where the first occurrence (dark vertical bar) of the activation condition doesn't lead to a check of the input sequence as we can forecast there won't be any problem. The second occurrence activates the automaton and provides a witness of a crash (triple vertical bar). We are thus reducing the number of simultaneous checks, this is quite feasible with observers (automata).

Figure 1.10: Artifact on invariant mode

Instead of trying to determine whether or not we have to activate concurrent checks of the property, we could allow only one instance of this check at a time, but accept more activations if they are not concurrent. This is the purpose of the iterative mode.

## 1.5.3 Iterative mode

The *iterative* modes sets a lock when an activation occurs. This lock prevents any reactivation of the same specification until it is released, and it is released when we can definitely agree on the specification.

The point is now to define when we are able to agree definitely on the specification, even if this one concerns an infinite word, as it is the case for  $\omega$ -words. Let's define a *finitely accepting state*, which is a state s such that:

- s is an accepting state.

- s has no outgoing transition, except a unique self loop labelled by true.

We can obviously state that whenever the automaton representing the specification to be verified reaches such a finitely accepting state the requirement is (finitely) fulfilled, recalling therefore Büchi 's acceptance criteria explained in section 1.3.1 which accepts any run as long as it infinitely often goes through an accepting state.

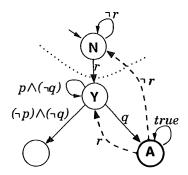

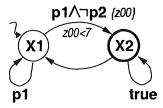

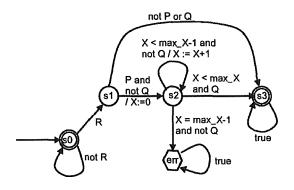

We show in figure 1.11 the finitely accepting states for the LTL formula  $p\ U\ q$  with the activation condition r. This automaton is composed of two parts, the first, above the dotted line, represents the activation condition, its state will remain active as long as the activation condition r is not met. This first part does not belong to the automaton. The second part is the main automaton, the specification, with 1 fair states (in bold) which fulfills the second property, it is the only finitely accepting state (hence labelled by A).

Figure 1.11: Determining finitely accepting states

We want to set and release a *lock* during the check, enabling a new activation only when the current one can't fail anymore.

Some states in which we can be sure of the result, even if the input sequence is infinite, are the finitely accepting states. We should thus release the lock whenever *entering* such a state. We could enhance this definition considering "finitely accepting strongly connected components (SCC)", i.e. SCC with only **true** labels, rather than states, this has not be done yet.

Such a behavior, of releasing the lock when entering any finitely accepting state is simply done through a modification of the transition relation.

The action of releasing the lock actually means to come back from any finitely accepting state either to

- waiting for the activation condition, if is not true yet.

- getting in the initial state of the automaton, if the activation condition already holds.

We show how  $\longrightarrow$  (using the notation described in 1.3.2) has to be modified to exhibit *release lock behavior* in figure 1.12, using the same LTL formula as in the previous example. The added heavy-dotted transition releases the lock, while the **true** self-loop of the finitely accepting state is now labelled be

29

the negation of the activation condition. Such a modification of the transition relation should be done from every finitely accepting states if there are more than one.

Figure 1.12: Iterative mode lock handling

## 1.6 Particular TBAs

The Timed Büchi Automata resulting from the unwinding procedure in section 1.4 are a bit particular. In this section we describe some restrictions that can be made on the formalism due to its particular unwound origin.

## 1.6.1 Activation mode

The activation mode is added to our (unwinding) TBA format as a comment, just as we told. This mere "annotation" will be considered later on, when we effectively check the property, but does not influence the specification at all.

## 1.6.2 Acyclic Automata

The unwinding procedure builds up the automaton using a total order on the locations, i.e. a location is unwound only when all its prerequisites have already been unwound (we refer to section 1.4.2). This way of doing will always provide us with a TBA that has no back-leading transition, and thus no cycle except self loops.

To highlight the fact that the TBA is cycle-free we remove all self-loops on the states, transforming each of them into an annotation that characterizes its state. This annotation is called *stable condition*.

Its meaning is simply it has to be fulfilled for the automaton to be allowed to remain in the current state. The semantics of a stable condition has been given in 1.3.3